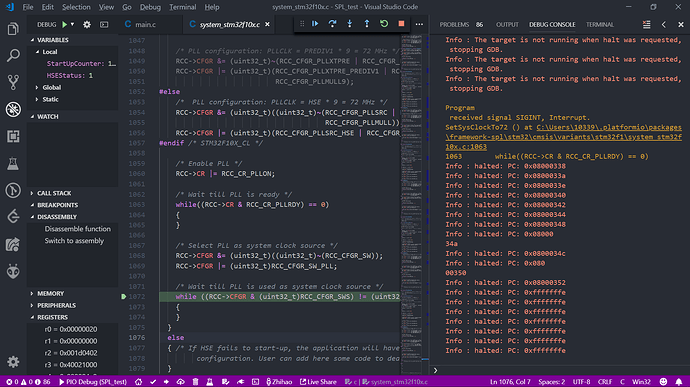

Hi, I’m using SPL for STM32VLDISCOVERY, which is not supported by Platform IO IDE. I’ve tried to configure an SPL framework manually by downloading SPL from ST official website and set up the directories in “framework-spl” folder just as the SPL framework for other boards does. However, there is still some problems on uploading the elf file to my board. The VS Code keeps popping up like “Error: no handler found” and although the files seemed to compile and upload successfully, there was no response on my board (I wrote a simple LED-blink program, but the LED was not blinking). I entered the debug mode to check it out and found that the program kept stuck at this line of code:

Any suggestions on how to add SPL framework manually to STM32VLDISCOVERY? Thanks!!

Plus: I’m using STlink for on-board debugging, and here is my platform.ini:

[env:disco_f100rb]

platform = ststm32

board = disco_f100rb

framework = spl

debug_tool = stlink

upload_protocol = stlink

build_flags = -DSTM32F10X_MD

I also configured the disco_100rb.json to be the following:

{

"build": {

"core": "stm32",

"cpu": "cortex-m3",

"extra_flags": "-DSTM32F100xB -DSTM32F10X_MD",

"f_cpu": "24000000L",

"mcu": "stm32f100rbt6",

"variant": "DISCO_F100RB"

},

"debug": {

"default_tools": [

"stlink"

],

"jlink_device": "STM32F100RB",

"onboard_tools": [

"stlink"

],

"openocd_board": "stm32vldiscovery",

"openocd_target": "stm32f1x",

"svd_path": "STM32F100xx.svd"

},

"frameworks": [

"arduino",

"mbed",

"stm32cube",

"spl"

],

"name": "ST STM32VLDISCOVERY",

"upload": {

"maximum_ram_size": 8192,

"maximum_size": 131072,

"protocol": "stlink",

"protocols": [

"jlink",

"stlink",

"blackmagic"

]

},

"url": "http://www.st.com/web/catalog/tools/FM116/SC959/SS1532/LN1848/PF250863",

"vendor": "ST"

}

and I modified the spl.py file:

#

# Target: Build SPL Library

#

extra_flags = env.BoardConfig().get("build.extra_flags", "")

src_filter_patterns = ["+<*>"]

if "STM32F40_41xxx" in extra_flags:

src_filter_patterns += ["-<stm32f4xx_fmc.c>"]

if "STM32F427_437xx" in extra_flags:

src_filter_patterns += ["-<stm32f4xx_fsmc.c>"]

elif "STM32F303xC" in extra_flags:

src_filter_patterns += ["-<stm32f30x_hrtim.c>"]

elif "STM32L1XX_MD" in extra_flags:

src_filter_patterns += ["-<stm32l1xx_flash_ramfunc.c>"]

elif "STM32F10X_MD" in extra_flags:

src_filter_patterns += [""]

I really have no idea on how to add an SPL manually, but I just tried to imitate the existing SPL framework. Any suggestions will help!