Actually, I don’t think this is possible with the APLL.

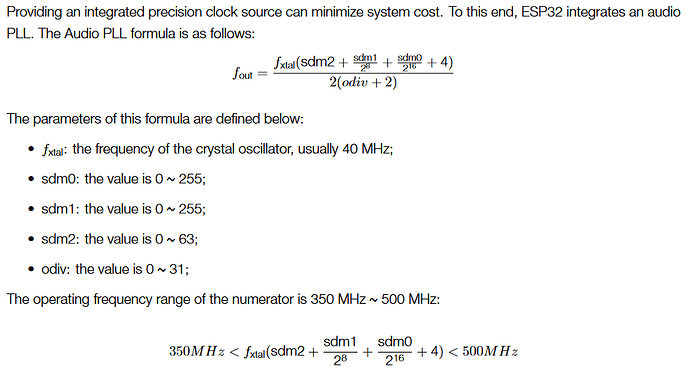

If the biggest value in the numerator can be 500 MHz and the smallest possible divisor can be 4 (setting odiv = 0), then the max output frequency of the APLL is only 500 / 4 = 125 MHz.

This would be divided by 2 to get CPU CLK, again divided by 2 to get APB clock, which would also be the max SPI clock, and that turns then into only 31.25 MHz.

That’s worse than the regular PLL that could do 40 MHz or 80MHz.

As such, 40MHz is probably the closest you can get, if you don’t do crazy assembly level, single cycle I/O bit-banging of the SPI line.