Hi,

first - I am new to ESP32 / PlatformIO.

I designed a board with module ESP32-S3-WROOM-1-N16R8, samples made by JLCPCB.

The module order code (JLCPCB or LCSC) is C2913202.

It should contain 16MB Flash + 8 MB PSRAM.

I created a new project, with board=Espressif ESP32-S3-BOX

because according to description of this project

“ESP32-S3-BOX comes with 16MB of QSPI flash and 8MB of Octal PSRAM”.

So I thought it is based on the same module.

main.cpp is a copy of example

/platformio/platform-espressif32/blob/master/examples/espidf-hello-world/src/hello_world_main.c

I made litle changes to print detailed info about “features” via this block of code:

// Print chip information

esp_chip_info_t chip_info;

esp_chip_info(&chip_info);

printf("chip_info: features=0x%08X, cores=%u, revision=%u\n",

chip_info.features, chip_info.cores, chip_info.revision);

// particular features

printf("EMB_FLASH...%s\n", (chip_info.features & CHIP_FEATURE_EMB_FLASH) ? "Y" : "n");

// Chip has embedded flash memory

printf("WIFI_BGN....%s\n", (chip_info.features & CHIP_FEATURE_WIFI_BGN) ? "Y" : "n");

// Chip has 2.4GHz WiFi

printf("BLE.........%s\n", (chip_info.features & CHIP_FEATURE_BLE) ? "Y" : "n");

// Chip has Bluetooth LE

printf("BT..........%s\n", (chip_info.features & CHIP_FEATURE_BT) ? "Y" : "n");

// Chip has Bluetooth Classic

printf("IEEE802154..%s\n", (chip_info.features & CHIP_FEATURE_IEEE802154) ? "Y" : "n");

// Chip has IEEE 802.15.4, low-rate wireless personal area network (LR-WPAN)

printf("EMB_PSRAM...%s\n", (chip_info.features & CHIP_FEATURE_EMB_PSRAM) ? "Y" : "n");

// Chip has embedded psram

// show model name

printf("chip model=%u ", (unsigned char)chip_info.model);

if (chip_info.model == CHIP_ESP32) printf("ESP32\n"); // 1

else if (chip_info.model == CHIP_ESP32S2) printf("ESP32-S2\n"); // 2

else if (chip_info.model == CHIP_ESP32S3) printf("ESP32-S3\n"); // 9

else if (chip_info.model == CHIP_ESP32C3) printf("ESP32-C3\n"); // 5

else if (chip_info.model == CHIP_ESP32H2) printf("ESP32-H2\n"); // 6

else printf("unknown\n");

// show flash size

printf("%dMB %s flash\n", spi_flash_get_chip_size() / (1024 * 1024),

(chip_info.features & CHIP_FEATURE_EMB_FLASH) ? "embedded" : "external");

// show size of PSRAM

multi_heap_info_t info;

heap_caps_get_info(&info, MALLOC_CAP_SPIRAM);

long unsigned int sizePSRAM;

sizePSRAM = (long unsigned int)(info.total_free_bytes + info.total_allocated_bytes);

printf("PSRAM size = %lu\n", sizePSRAM);

(also combined with 2 tasks

- UART echo example:

/platformio/platform-espressif32/blob/master/examples/espidf-peripherals-uart/src/uart_echo_example_main.c - LED flashing)

It all works, important is, it prints:

chip_info: features=0x00000012, cores=2, revision=0

EMB_FLASH...n

WIFI_BGN....Y

BLE.........Y

BT..........n

IEEE802154..n

**EMB_PSRAM...n**

chip model=9 ESP32-S3

16MB external flash

**PSRAM size = 0**

The initial debug text ESP is (problematic lines highlighted):

ELF file SHA256: ddccacd149a73633

Rebooting…

ESP-ROM:esp32s3-20210327

Build:Mar 27 2021

rst:0xc (RTC_SW_CPU_RST),boot:0x29 (SPI_FAST_FLASH_BOOT)

Saved PC:0x403758c4

SPIWP:0xee

mode:DIO, clock div:1

load:0x3fcd0108,len:0x1648

load:0x403b6000,len:0xb7c

load:0x403ba000,len:0x2f74

SHA-256 comparison failed:

Calculated: ecd0239307e887b897a8687fd0c440d7911a2c55eb2a7916905ddd04eb8b1508

Expected: 094d10123a151508d62769f8aa43ccd31e5757064977a5c521168ba85be6acb5

Attempting to boot anyway…

entry 0x403b6248

I (47) boot: ESP-IDF 4.4.1 2nd stage bootloader

I (48) boot: compile time 20:26:11

I (48) boot: chip revision: 0

I (49) boot.esp32s3: Boot SPI Speed : 80MHz

I (54) boot.esp32s3: SPI Mode : DIO

I (59) boot.esp32s3: SPI Flash Size : 16MB

I (63) boot: Enabling RNG early entropy source…

I (69) boot: Partition Table:

I (72) boot: ## Label Usage Type ST Offset Length

I (80) boot: 0 nvs WiFi data 01 02 00009000 00006000

I (87) boot: 1 phy_init RF data 01 01 0000f000 00001000

I (95) boot: 2 factory factory app 00 00 00010000 00100000

I (102) boot: End of partition table

I (106) esp_image: segment 0: paddr=00010020 vaddr=3c020020 size=07ba8h ( 31656) map

I (121) esp_image: segment 1: paddr=00017bd0 vaddr=3fc90640 size=026fch ( 9980) load

I (125) esp_image: segment 2: paddr=0001a2d4 vaddr=40374000 size=05d44h ( 23876) load

I (137) esp_image: segment 3: paddr=00020020 vaddr=42000020 size=1774ch ( 96076) map

I (158) esp_image: segment 4: paddr=00037774 vaddr=40379d44 size=068f0h ( 26864) load

I (164) esp_image: segment 5: paddr=0003e06c vaddr=50000000 size=00010h ( 16) load

I (169) boot: Loaded app from partition at offset 0x10000

I (169) boot: Disabling RNG early entropy source…

I (186) cpu_start: Pro cpu up.

I (186) cpu_start: Starting app cpu, entry point is 0x40375454

I (151) cpu_start: App cpu up.

I (200) cpu_start: Pro cpu start user code

I (201) cpu_start: cpu freq: 160000000

I (201) cpu_start: Application information:

I (203) cpu_start: Project name: ESPs3b

I (208) cpu_start: App version: 1

I (213) cpu_start: Compile time: Sep 29 2022 20:25:10

I (219) cpu_start: ELF file SHA256: ddccacd149a73633…

I (225) cpu_start: ESP-IDF: 4.4.1

I (229) heap_init: Initializing. RAM available for dynamic allocation:

I (237) heap_init: At 3FC93760 len 0004C8A0 (306 KiB): D/IRAM

I (243) heap_init: At 3FCE0000 len 0000EE34 (59 KiB): STACK/DRAM

I (250) heap_init: At 3FCF0000 len 00008000 (32 KiB): DRAM

I (256) heap_init: At 600FE000 len 00002000 (8 KiB): RTCRAM

I (263) spi_flash: detected chip: gd

I (267) spi_flash: flash io: dio

I (271) sleep: Configure to isolate all GPIO pins in sleep state

I (277) sleep: Enable automatic switching of GPIO sleep configuration

I (285) cpu_start: Starting scheduler on PRO CPU.

I (0) cpu_start: Starting scheduler on APP CPU.

There is no single line about PSRAM or SPIRAM.

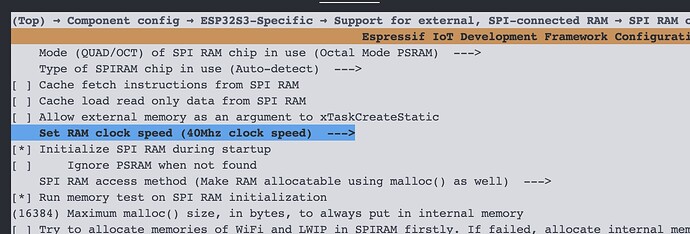

I found configuration file sdkconfig.esp32s3box

contains line: #CONFIG_ESP32S3_SPIRAM_SUPPORT is not set

so I added a line to platformio.ini that I hoped will fix it:

platformio.ini :

[env:esp32s3box]

platform = espressif32

board = esp32s3box

framework = espidf

monitor_speed = 115200

upload_port = COM12

monitor_port = COM12

build_flags = -D CONFIG_ESP32_SPIRAM_SUPPORT=1

also tried these lines, but no difference:

build_flags = -D CONFIG_ESP32S3_SPIRAM_SUPPORT=1

build_flags = -DBOARD_HAS_PSRAM -mfix-esp32-psram-cache-issue

So, why the PSRAM is not detected ?

I only guess problem is one of following:

a) wrong “board” selection - is there any better/correct choice ?

(I have also tried Board: Adafruit Feather ESP32-S3 2MB PSRAM, still no success with PSRAM)

b) the module really doesn’t contain PSRAM - how to recognise is reliably ?

(on the bottom of module is label M0N16R8)

c) maybe some other PlatformIO or esp-idf setting must be changed - what and how ?

Any ideas are welcome, or link to stuff I should study, or similar project that works.